| Das eBook Angewandte Mikroelektronik wurde von Hans Lohninger zur Unterstützung verschiedener Lehrveranstaltungen geschrieben. Weitere Informationen finden sie hier. |

|

Home  Digitaltechnik Digitaltechnik  Boole'sche Algebra Boole'sche Algebra  Karnaugh-Veitch Diagramme Karnaugh-Veitch Diagramme |

||||||||

| Siehe auch: Synthese logischer Funktionen | ||||||||

|

||||||||

Karnaugh-Veitch Diagramme

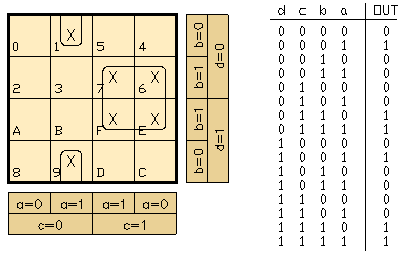

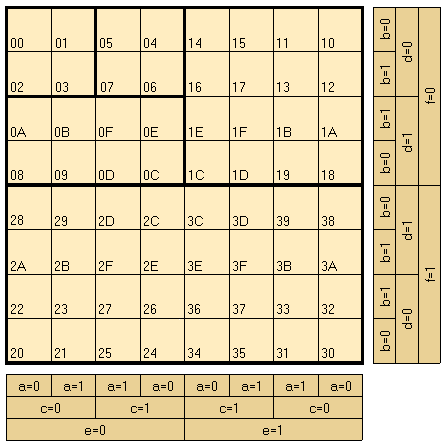

Im KV-Diagramm wird die Wahrheitstafel nur in etwas veränderter Form aufgetragen. Das Diagramm hat die Form eines Schachbrettes, wobei jedes Feld des Schachbrettes eine hexadezimale Nummer trägt, die der Bitkombination der Wahrheitstafel entspricht. Die Felder sind so angeordnet, dass sich jedes benachbarte Feld nur durch jeweils eine Variable unterscheidet. Je nachdem, wie viele Eingangsvariablen vorhanden sind, ist das KV-Diagramm unterschiedlich groß. Die Grenzen für 2 bis 6 Eingangsvariablen sind in folgender Abbildung mit stärkeren Linien markiert. Die Verbindung zwischen KV-Diagramm und Wahrheitstafel ergibt sich wie folgt: Jede Eingangsvariable wird mit einem Buchstaben, beginnend mit a, von rechts nach links benannt. Jede Zeile der Wahrheitstafel entspricht nun jenem Feld des KV-Diagramms, dessen hexadezimale Nummer der Bitkombination der Eingangsvariablen entspricht.

Die Anwendung des KV-Diagramms zur Reduktion der logischen Gleichung geschieht nun so:

Ein Beispiel soll die eben geschilderte Vorgangsweise verdeutlichen: Es soll eine Schaltung konstruiert werden, deren Funktion der unten abgebilteten Wahrheitstafel entspricht. Es wird dazu im ersten Schritt für jede Zeile, die in der Ausgangsspalte der Wahrheitstafel eine Eins enthält, das entsprechenden Feld des KV-Diagramms angekreuzt (Felder 1, 6, 7, 9, E, und F). Dann werden möglichst große Blöcke gebildet. Für unser Beispiel ergeben sich zwei Blöcke, einer mit vier Feldern und einer mit zwei Feldern. Für diese Blöcke ergeben sich folgende logische Ausdrücke: b Diese werden im letzten Schritt zum Gesamtausdruck b zusammengefasst. Man sieht, dass die Eingangsvariable d keinen Einfluss auf die Ausgangsvariable hat und in der Schaltung die Signalleitung d weggelassen werden kann (außer sie wird für andere Zwecke benötigt).

|

||||||||

Home  Digitaltechnik Digitaltechnik  Boole'sche Algebra Boole'sche Algebra  Karnaugh-Veitch Diagramme Karnaugh-Veitch Diagramme |

||||||||

Last Update: 2008-05-31

c und a

c und a