| Das eBook Angewandte Mikroelektronik wurde von Hans Lohninger zur Unterstützung verschiedener Lehrveranstaltungen geschrieben. Weitere Informationen finden sie hier. |

|

Home  Experimente Experimente  Interfaces zwischen Analog und Digitaltechnik Interfaces zwischen Analog und Digitaltechnik  Aufbau eines Spannungs-Frequenzwandlers Aufbau eines Spannungs-Frequenzwandlers |

|||

| Siehe auch: Spannungs-Frequenz-Wandler | |||

|

|||

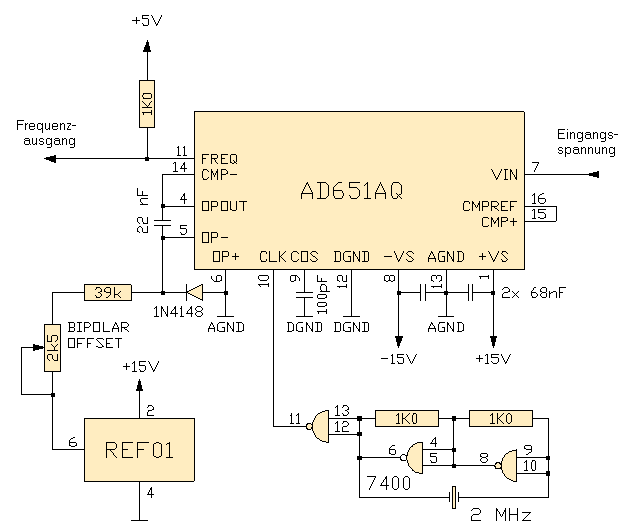

Experiment: Aufbau eines UF-Wandlers

In diesem Experiment soll ein synchroner UF-Wandler aufgebaut werden, der im Gegensatz zu den sonst üblichen UF-Wandlern eine sehr gute Stabilität aufweist. Dazu wird der VCO AD651 verwendet, der seine Ausgangsfrequenz von einer externen (quarzstabilisierten) Referenzfrequenz ableitet. Die im Folgenden beschriebene Schaltung setzt dieses Bauelement zur Wandlung von bipolaren Signalen zwischen +/- 5V ein. Es wird entsprechend eine Frequenz zwischen 0 Hz (= -5V) und 1 MHz (= +5V) erzeugt. Die Auflösung beträgt ca. 20 Bit (bei 1 s Messzeit), die Linearität des Wandler ist bei der gegebenen Referenzfrequenz von 2 MHz etwa 0.02 % (ca. 12 Bit). Eine bessere Linearität wird erreicht, wenn man die Referenzfrequenz auf 200 kHz senkt; man erreicht dann eine Linearität von ca. 16 Bit.

Die Ausgangsfrequenz kann mit einem handelsüblichen Frequenzzähler gemessen werden. Möchte man einen eigenen Zähler anschließen, so empfiehlt es sich, die Torzeit des dann notwendigen Gatters aus der Referenzfrequenz des VCOs abzuleiten. Dies führt zur Unabhängigkeit der Messung von Schwankungen der Referenzfrequenz und erhöht die Stabilität noch weiter.

|

|||

Home  Experimente Experimente  Interfaces zwischen Analog und Digitaltechnik Interfaces zwischen Analog und Digitaltechnik  Aufbau eines Spannungs-Frequenzwandlers Aufbau eines Spannungs-Frequenzwandlers |

|||

Last Update: 2008-05-31