| Befehl |

Kurzbeschreibung |

Erläuterung |

Flags |

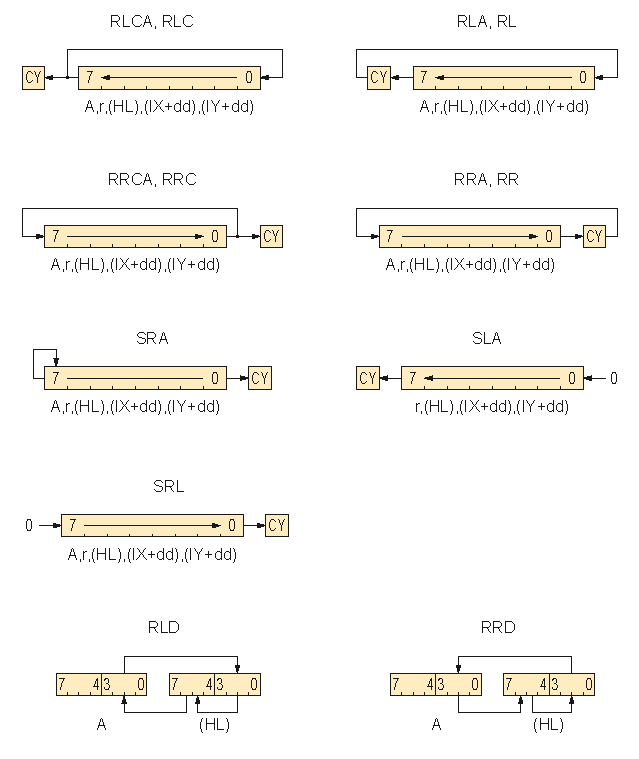

RLCA |

Rotation nach links. |

Der Inhalt des Akkumulators wird um eine Stelle nach links verschoben, wobei Bit 7 sowohl in das Carry-Flag als auch in Bit 0 übertragen wird. |

H=0 |

N=0 |

C = Bit 7 des Akkumulators |

alle anderen Flags bleiben unverändert |

RLA |

Rotation nach links über Carry-Flag. |

Der Inhalt des Akkumulators wird um eine Stelle nach links verschoben, wobei Bit 7 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 0. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 7 des Akkumulators |

alle anderen Flags bleiben unverändert |

RRCA |

Rotation nach rechts. |

Der Inhalt des Akkumulators wird um eine Stelle nach rechts verschoben, wobei Bit 0 sowohl in das Carry-Flag als auch in Bit 7übertragen wird. |

H=0 |

N=0 |

C = Bit 0 des Akkumulators |

alle anderen Flags bleiben unverändert |

RRA |

Rotation nach rechts über Carry-Flag. |

Der Inhalt des Akkumulators wird um eine Stelle nach rechts verschoben, wobei Bit 0 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 7. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 0 des Akkumulators |

alle anderen Flags bleiben unverändert |

RLC r |

Rotation nach links. |

Der Inhalt des Registers r wird um eine Stelle nach links verschoben, wobei Bit 7 sowohl in das Carry-Flag als auch in Bit 0 übertragen wird. |

H=0 |

N=0 |

C = Bit 7 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RLC (HL) |

Rotation nach links. |

Der Inhalt der durch das Register HL adressierten Speicherzelle wird um eine Stelle nach links verschoben, wobei Bit 7 sowohl in das Carry-Flag als auch in Bit 0 übertragen wird. |

H=0 |

N=0 |

C = Bit 7 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RLC (IX+dd)

RLC (IY+dd) |

Rotation nach links.

|

Der Inhalt der durch IX+dd bzw. IY+dd adressierten Speicherzelle wird um eine Stelle nach links verschoben, wobei Bit 7 sowohl in das Carry-Flag als auch in Bit 0 übertragen wird. |

H=0 |

N=0 |

C = Bit 7 von (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RL r |

Rotation nach links über Carry-Flag. |

Der Inhalt des Registers r wird um eine Stelle nach links verschoben, wobei Bit 7 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 0. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 7 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RL (HL) |

Rotation nach links über Carry-Flag. |

Der Inhalt der durch HL adressierten Speicherzelle wird um eine Stelle nach links verschoben, wobei Bit 7 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 0. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 7 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RL (IX+dd)

RL (IY+dd) |

Rotation nach links über Carry-Flag.

|

Der Inhalt der durch IX+dd bzw. IY+dd adressierten Speicherzelle wird um eine Stelle nach links verschoben, wobei Bit 7 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 0. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 7 der Speicherzelle (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RRC r |

Rotation nach rechts. |

Der Inhalt des Registers r wird um eine Stelle nach rechts verschoben, wobei Bit 0 sowohl in das Carry-Flag als auch in Bit 7 übertragen wird. |

H=0 |

N=0 |

C = Bit 0 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RRC (HL) |

Rotation nach rechts. |

Der Inhalt der Speicherzelle, die durch das Register HL adressiert wird, wird um eine Stelle nach rechts verschoben, wobei Bit 0 sowohl in das Carry-Flag als auch in Bit 7 übertragen wird. |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RRC (IX+dd)

RRC (IY+dd) |

Rotation nach rechts.

|

Der Inhalt der Speicherzelle, die durch (IX+dd) bzw. durch(IY+dd) adressiert wird, wird um eine Stelle nach rechts verschoben, wobei Bit 0 sowohl in das Carry-Flag als auch in Bit 7übertragen wird. |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RR r |

Rotation nach rechts über Carry-Flag. |

Der Inhalt des Registers r wird um eine Stelle nach rechts verschoben, wobei Bit 0 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 7. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 0 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RR (HL) |

Rotation nach rechts über Carry-Flag. |

Der Inhalt der durch HL adressierten Speicherzelle wird um eine Stelle nach rechts verschoben, wobei Bit 0 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 7. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RR (IX+dd)

RR (IY+dd) |

Rotation nach rechts über Carry-Flag.

|

Der Inhalt der durch IX+dd bzw. IY+dd adressierten Speicherzelle wird um eine Stelle nach rechts verschoben, wobei Bit 0 in das Carry-Flag übertragen wird und das Carry-Flag in Bit 7. Dieser Rotationsbefehl schließt also das Carry-Flag ein (Rotation über neun Bits). |

H=0 |

N=0 |

C = Bit 0 von (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SLA r |

Arithmetisches Schieben nach links. |

Der Inhalt des Registers r wird um eine Binärstelle nach links verschoben, wobei Bit 0 mit null aufgefüllt wird und Bit 7 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 7 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SLA (HL) |

Arithmetisches Schieben nach links. |

Der Inhalt der Speicherzelle, die durch das Register HL adressiert wird, wird um eine Binärstelle nach links verschoben, wobei Bit 0 mit null aufgefüllt wird und Bit 7 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 7 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SLA (IX+dd)

SLA (IY+dd) |

Arithmetisches Schieben nach links.

|

Der Inhalt der Speicherzelle, die durch (IX+dd) bzw. (IY+dd) adressiert wird, wird um eine Binärstelle nach links verschoben, wobei Bit 0 mit null aufgefüllt wird und Bit 7 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 7 der Speicherzelle (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRA r |

Arithmetisches Schieben nach rechts. |

Der Inhalt des Registers r wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 dupliziert wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRA (HL) |

Arithmetisches Schieben nach rechts. |

Der Inhalt der Speicherzelle, die durch das Register HL adressiert wird, wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 dupliziert wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRA (IX+dd)

SRA (IY+dd) |

Arithmetisches Schieben nach rechts.

Arithmetisches Schieben nach rechts. |

Der Inhalt der Speicherzelle, die durch (IX+dd) bzw. (IY+dd) adressiert wird, wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 dupliziert wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 von (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRL r |

Logisches Schieben nach rechts. |

Der Inhalt des Registers r wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 auf null gesetzt wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 des Registers r |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRL (HL) |

Logisches Schieben nach rechts. |

Der Inhalt der Speicherzelle, die durch das Register HL adressiert wird, wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 auf null gesetzt wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (HL) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

SRL (IX+dd)

SRL (IY+dd) |

Logisches Schieben nach rechts.

|

Der Inhalt der Speicherzelle, die durch (IX-dd) bzw. (IY+dd) adressiert wird, wird um eine Binärstelle nach rechts verschoben, wobei Bit 7 auf null gesetzt wird und Bit 0 in das Carry-Flag kopiert wird. |

H=0 |

N=0 |

C = Bit 0 der Speicherzelle (IX+dd) bzw. (IY+dd) |

S=1, wenn Ergebnis negativ, sonst S=0 |

Z=1, wenn Ergebnis gleich null, sonst Z=0 |

P/V=1, wenn Parität gerade, sonst P/V=0 |

RLD |

4-Bit-Rotation nach links. |

Bei dieser 4-Bit-Rotation werden der Akkumulator und eine durch HL adressierte Speicherzelle verändert. Die unteren vier Bits der Speicherzelle werden in die obere Hälfte der Zelle kopiert. Der zuvor gerettete Inhalt der oberen Hälfte der Speicherzelle wird in die untere Hälfte des Akkumulators kopiert und dessen(zuvor gerettete) untere Hälfte wird in die untere Hälfte der Speicherzelle kopiert. Diese Operation kann vorteilhaft bei der Verarbeitung von BCD-Zahlen verwendet werden. |

H=0 |

N=0 |

C unverändert |

S=1, wenn Akkumulator negativ, sonst S=0 |

Z=1, wenn Akkumulator gleich null, sonst Z=0 |

P/V=1, wenn die Parität im Akkumulator gerade |

RRD |

4-Bit-Rotation nach rechts. |

Bei dieser 4-Bit-Rotation werden der Akkumulator und eine durch HL adressierte Speicherzelle verändert. Die unteren vier Bits der Speicherzelle werden in die untere Hälfte des Akkumulators kopiert. Der zuvor gerettete Inhalt der unteren Hälfte des Akkumulators wird in die obere Hälfte der Speicherzelle kopiert und die (zuvor gerettete) obere Hälfte der Speicherzelle wird in die untere Hälfte der Speicherzelle kopiert. Diese Operation kann vorteilhaft bei der Verarbeitung von BCD-Zahlen verwendet werden. |

H=0 |

N=0 |

C unverändert |

S=1, wenn Akkumulator negativ, sonst S=0 |

Z=1, wenn Akkumulator gleich null, sonst Z=0 |

P/V=1, wenn Parität im Akkumulator gerade |

Mikroprozessoren

Mikroprozessoren  Der Prozessor Z80

Der Prozessor Z80  Befehlssatz

Befehlssatz  Rotations- und Schiebebefehle

Rotations- und Schiebebefehle

Mikroprozessoren

Mikroprozessoren  Der Prozessor Z80

Der Prozessor Z80  Befehlssatz

Befehlssatz  Rotations- und Schiebebefehle

Rotations- und Schiebebefehle