Pinbelegung Z80

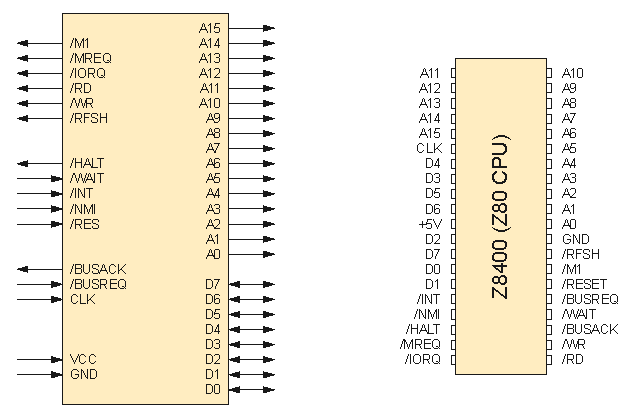

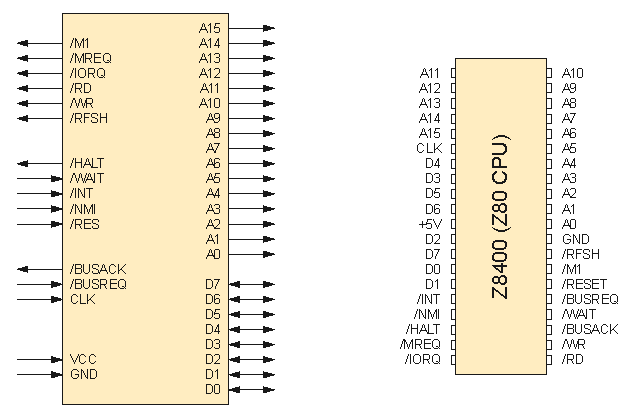

Folgende Abbildung zeigt die Pinfunktionen und das Anschlussschema des Bausteins. Die Anschlüsse können in mehrere Gruppen zusammengefasst werden, die im Folgenden kurz besprochen werden sollen.

|

| Z80-CPU Anschlussschema |

Zur Stromversorgung benötigt der Baustein eine einzige Spannung von 5 V. Die Stromaufnahme beträgt je nach verwendeter Halbleitertechnologie und Taktfrequenz zwischen 10 und 200 mA.

Datenbus

Der Datenbus besteht aus acht bidirektionalen Datenleitungen D0 - D7 , auf denen der Transfer von Daten und Befehlen zwischen dem Mikroprozessor und der Außenwelt vor sich geht. D0 ist das LSB, D7 das MSB. Die Datenleitungen sind als Tri-State-Anschlüsse ausgeführt.

Adressbus

Der Adressbus besteht aus 16 Leitungen A0 - A15 , mit denen maximal 64 KByte adressiert werden können. Zur Adressierung von größeren Speichern müssen durch externe Hardware (z.B. Bank Switching oder MMU) zusätzliche Adressleitungen angesteuert werden. Die Adressleitungen sind Tri-State-Leitungen, damit eventuelle externe Prozessoren auf den Bus zugreifen können (siehe /BUSRQ).

System-Steuerleitungen

Die Steuerleitungen dienen zur Kontrolle des angeschlossenen Systems. Folgende Anschlüsse sind dazu vorgesehen:

/M1 |

Machine Cycle One (Ausgang, aktiv = LOW).

/M1 zeigt an, dass der aktuelle Maschinenzyklus einen Befehl aus dem Speicher holt und zur Ausführung bringt. Bei Befehlen mit zwei Befehlsbytes wird /M1 zweimal hintereinander auf LOW gebracht. /M1 wird auch zur Kennzeichnung eines Interrupt-Acknowledge-Zyklus zusammen mit dem Pin /IORQ verwendet. |

/MREQ |

Memory Request (Tri-State-Ausgang, aktiv = LOW).

Ein LOW Signal auf der Leitung /MREQ zeigt an, dass auf dem Adressbus eine gültige Adresse anliegt und entweder ein Byte gelesen (/RD=LOW) oder geschrieben (/WR=LOW) werden soll. |

/WR |

Write (Tri-State-Ausgang, aktiv = LOW).

Ein LOW-Signal auf der Leitung /WR zeigt an, dass der Mikroprozessor am Datenbus gültige Daten ausgibt, die entweder in den Speicher oder in einen Peripheriebaustein geschrieben werden sollen. |

/RD |

Read (Tri-State-Ausgang, aktiv = LOW).

Der Pin /RD wird von der CPU aktiviert, wenn Daten oder Befehle zwischen Speicher bzw. Peripherie und der CPU transferiert werden sollen. |

/REF |

Refresh (Ausgang, aktiv = LOW).

/REF zeigt an, dass die CPU auf den Adressleitungen A0-A6 eine gültige Refresh-Adresse gelegt hat. Mit dieser Refresh-Adresse soll beim Auftreten von /MREQ=LOW ein Refresh aller RAMs durchgeführt werden. |

/HALT |

Halt (Ausgang, aktiv = LOW).

/HALT zeigt an, dass die CPU den Befehl HALT ausgeführt hat und nun auf einen Interrupt (/NMI oder /INT) wartet, um wieder weiterzuarbeiten. Während der Haltperiode werden fortlaufend NOP-Befehle (no operation) ausgeführt, um den Refresh der Speicher zu gewährleisten. |

/IORQ |

Input Output Request (Ausgang, aktiv = LOW).

Wenn dieses Signal auf LOW geht, enthält die untere Hälfte des Adressbusses eine gültige I/O-Adresse. Mit Hilfe der Signale /RD und /WR werden dann Daten geschrieben oder gelesen. /IORQ wird auch in einem Interrupt-Acknowledge-Zyklus (zusammen mit /M1) eingesetzt. |

CPU-Steuerleitungen

/WAIT |

Wait (Eingang, aktiv = LOW).

Wird die Leitung /WAIT aktiviert, so wird die CPU während eines Speicher- oder eines I/O-Zugriffs angehalten, bis /WAIT wieder auf HIGH geht. Mit diesem Signal können langsame Speicher oder Peripheriebausteine mit einer zu schnellen CPU synchronisiert werden. Das /WAIT-Signal kann auch dazu verwendet werden, die CPU im Single-Step-Verfahren zu betreiben. ACHTUNG !! Solange die CPU im WAIT-Zustand ist, wird der Refresh unterdrückt. |

/RESET |

Reset (Eingang, aktiv = LOW).

Ist dieser Anschluss aktiviert, wird die CPU initialisiert, wobei der Programmzähler auf null gesetzt, der maskierbare Interrupt deaktiviert, der Interruptmodus auf null gesetzt und die Register I und R mit dem Wert null geladen werden. |

/BUSRQ |

Bus Request (Eingang, aktiv = LOW).

Das Signal /BUSRQ wird dazu verwendet, der CPU mitzuteilen, dass sie den Adressbus, den Datenbus und die Kontrollsignale mit Tri-State-Ausgang in den hochohmigen Zustand schaltet, damit ein anderer Prozessor auf den Bus zugreifen kann. Wenn /BUSRQ aktiviert worden ist, setzt die CPU nach der Beendigung des aktuellen Maschinenzyklus diese Leitungen in den hochohmigen Zustand und zeigt dies durch Aktivierung der Leitung /BUSAK an. |

/BUSAK |

Bus Acknowledge (Ausgang, aktiv = LOW).

Zeigt an, dass der Busanforderung (siehe /BUSREQ) eines anderen Prozessors stattgegeben wurde und die entsprechenden Busleitungen sich im hochohmigen Zustand befinden. ACHTUNG !! Während /BUSAK aktiv ist, erfolgt kein Refresh der dynamischen RAMs. |

CLK |

Clock (Eingang).

Der Anschluss CLK dient zur Synchronisation der internen Abläufe. Der Takt wird extern erzeugt und bestimmt die Arbeitsgeschwindigkeit des Mikroprozessors. Der Takt darf eine gewisse Maximalfrequenz (2.5 bis 8 MHz) nicht überschreiten, die in der Bauteilspezifikation angegeben ist. Außerdem darf diese Frequenz auch einen Minimalwert von 250 kHz nicht unterschreiten, da sonst die Register ihren Inhalt verlieren würden. |

Interruptleitungen

/INT |

Interrupt Request (Eingang, aktiv = LOW).

Am Anschluss /INT können externe Bausteine eine Interruptanforderung an die CPU abgeben. Diese Anforderung wird akzeptiert, wenn das Interrupt-Enable-Flip-Flop auf 'Enable' steht und das /BUSRQ-Signal nicht aktiv ist. Der genaue Ablauf eines Interruptzyklus und die verschiedenen Arten der Interruptsteuerung sind im Kapitel Interruptverarbeitung beschrieben. |

/NMI |

Non Maskable Interrupt Request (Eingang, aktiv = negative Flanke).

Die nicht maskierbare Interruptanforderung hat eine höhere Priorität als die maskierbare (/INT) und wird immer am Ende eines Befehls angenommen. Beim Auftreten eines Signals an /NMI wird die CPU gezwungen, an die Stelle $0066 im Adressraum zu springen und dort die Programmausführung fortzusetzen. ACHTUNG!! Ein permanentes/WAIT-Signal verhindert die Beendigung eines Befehls und damit auch die Ausführung des NMI. Zur genaueren Beschreibung siehe Interruptverarbeitung. |

|

Mikroprozessoren

Mikroprozessoren  Der Prozessor Z80

Der Prozessor Z80  Pinbelegung

Pinbelegung

Mikroprozessoren

Mikroprozessoren  Der Prozessor Z80

Der Prozessor Z80  Pinbelegung

Pinbelegung