| Das eBook Angewandte Mikroelektronik wurde von Hans Lohninger zur Unterstützung verschiedener Lehrveranstaltungen geschrieben. Weitere Informationen finden sie hier. |

|

Home  Anhang Anhang  Platinenlayouts Platinenlayouts  Platine SERPAR Platine SERPAR |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Siehe auch: Platinenlayouts | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Platine SERPAR

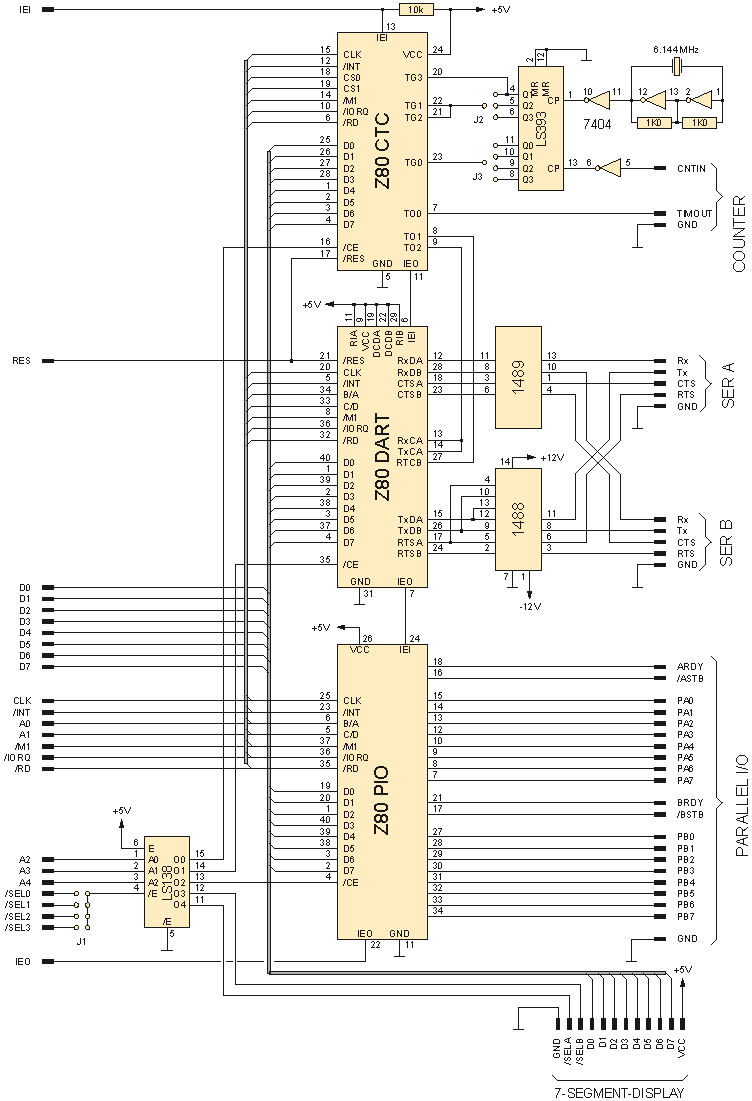

Die Platine SERPAR wurde als Erweiterungskarte für das Minimalsystem uP1 entwickelt. Die Karte wird auf einen der Busstecker der Platine uP1 gesteckt. Sie enthält einen Timer (Z80 CTC), zwei serielle Schnittstellen (Z80 DART), eine Parallelschnittstelle (Z80 PIO) und einen Anschluss an den I/O-Bus, um eine 7-Segment-Anzeige anschließen zu können. In der Abbildung ist der Schaltplan der Karte dargestellt. Die Karte belegt 32 aufeinander folgende Adressen im IO-Adressraum der Platine uP1, deren Beginn durch Jumper J2 festgelegt wird. Für alle in diesem Buch beschriebenen Experimente muss Jumper J2 mit /SEL0 verbunden sein. In der folgenden Tabelle sind die vier möglichen Basisadressen aufgeführt:

Von den 32 Adressen werden aber nur 14 Adressen belegt, die sich folgendermaßen aufteilen (alle Adressangaben beziehen sich auf die über Jumper J2 eingestellte Basisadresse):

Die Karte unterstützt voll den Z80-Interruptmodus (IM 2) der CPU, wobei die Priorisierung der Interrupts über eine Daisy-Chain erfolgt. Der Timer hat hierbei die höchste Priorität, der PIO die niedrigste.

CTC Der CTC wird von einem eigenen Quarzoszillator versorgt, der mit einer Frequenz von 6.144 MHz schwingt. Diese Frequenz ist sowohl für die Baudratenerzeugung als auch für Timingzwecke ausgezeichnet geeignet, da sie sich aus folgenden Faktoren zusammensetzt: 214 * 3 * 53. Die Frequenz des Quarzgenerators wird über einen 4-Bit-Teiler (LS393) geteilt. Drei dieser vier Frequenzen sind über den Jumper (J4) auswählbar und werden den Kanälen 1 und 2 des CTC zugeführt, die für die Baudratenerzeugung der DART zuständig sind. Außerdem wird die Frequenz 1.536 MHz dem Kanal 3 des CTC zugeführt, der als universeller Timer verwendet werden kann. Kanal 0 des CTC wird über den Eingang CNTIN und den Vorteiler angesteuert, um als universeller Zähler verwendet werden zu können. Zu beachten ist, dass die maximale Eingangsfrequenz des Teilers am Pin TG0 (Pin 23) die halbe Frequenz des Signals CLK sein darf (also 2 MHz). DART Die zwei voneinander unabhängigen Kanäle des DART werden über die RS-232-Treiber 1489 und 1488 auf die Stecker SERA und SERB gelegt. Die beiden seriellen Schnittstellen stellen zu den Datenleitungen jeweils zwei Handshake-Leitungen zur Verfügung, so dass eine Vierdraht-Leitung mit den Signalen Rx, Tx, CTS und RTS implementiert ist. Die Baudraten werden wie oben beschrieben mit den CTC-Kanälen 1 und 2 erzeugt. PIO Die PIO hat alle IO-Anschlüsse ohne Treiber auf den Stecker gelegt, so dass alle Betriebsarten der PIO voll ausgeschöpft werden können. Möchte man mit der PIO lange Leitungen treiben, sind jedoch Treiberbausteine zu verwenden. 7SGDSP Dieser Anschluss dient zum Betrieb des sechsstelligen 7-Segment-Displays (Platine 7SGDSP). Es sind alle Steuersignale und die Versorgungsspannung so an den Stecker geführt, dass das Display direkt mit einem Flachbandkabel angeschlossen werden kann (siehe auch Beschreibung der Platine 7SGDSP). Layout und Pinbelegung Die Abbildung zeigt den Bestückungsplan der Platine SERPAR und die Pinbelegung der I/O-Anschlüsse. Die folgende Stückliste hilft beim Aufbau der Platine.

Sonstiges:

Layout und Bestückungsplan der Platine

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Home  Anhang Anhang  Platinenlayouts Platinenlayouts  Platine SERPAR Platine SERPAR |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Last Update: 2008-05-31